El salto a Zen 4 no se producirá este año, pero AMD ya tiene una respuesta para los Alder Lake de Intel. Como se anunció en Computex a principios de este verano, AMD actualizará sus procesadores Zen 3 con el 3D V-Cache a principios de 2022, y esto debería ser suficiente para igualar el campo de juego contra Intel, al menos hasta que se lance la siguiente generación a finales de 2022. En el simposio anual Hot Chips, AMD proporcionó recientemente más detalles sobre el funcionamiento de 3D V-Cache y también ofreció un avance de sus futuras aplicaciones de apilamiento 3D.

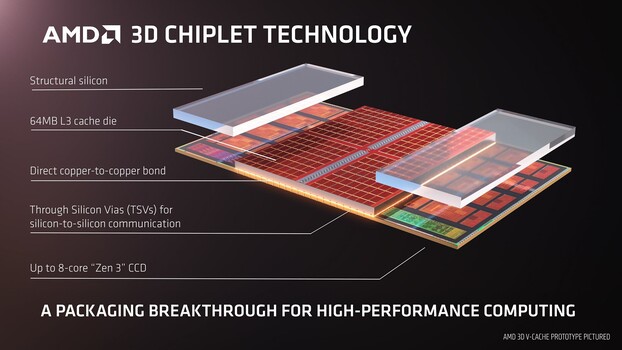

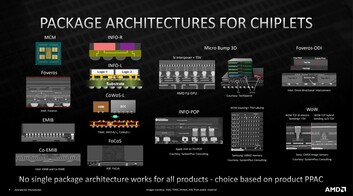

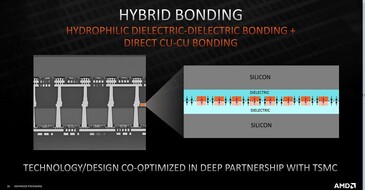

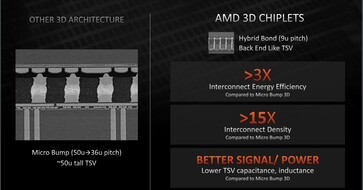

AMD está implementando un paquete de chips 3D Micro Bump de 9 micras para el V-Cache a través de una vía de silicio (TSV). Aunque sólo es 1 micra más fino que el paquete Foveros 3D de Intel que se utilizará para producir los procesadores Alder Lake, se dice que los Micro Bumps de AMD ofrecen más de 3 veces la eficiencia energética de la interconexión y 15 veces la densidad de interconexión y la capacitancia/inductancia. La actual tecnología TSV que actúa como conexión vertical entre obleas o entre troqueles no ofrece demasiados enlaces, pero, en el futuro, el paso de los TSV será cada vez más refinado, permitiendo diseños de apilamiento 3D más complejos. V-Cache, por ejemplo, permite una comunicación completa de silicio a silicio (DRAM en CPU / CPU en CPU) mediante enlaces directos de cobre a cobre. Esto permite añadir 64 MB de caché L3 a la cantidad existente, lo que se supone que proporciona un aumento del rendimiento del 15% en los juegos y del 19% en las aplicaciones de creación de contenidos.

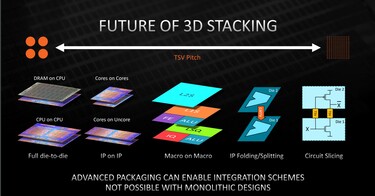

Los pasos más finos de los TSV permitirán complejas técnicas de apilamiento en 3D, como IP sobre IP (núcleos sobre núcleos / núcleos sobre un núcleo), macro sobre macro (SoCs sobre SoCs), y eventualmente incluso el plegado/división de IP y el corte de circuitos. Los requisitos de energía también se reducirán en más de 3 veces. Probablemente veremos la primera aplicación de la técnica de IP sobre IP con los núcleos de la GPU RDNA2 apilados sobre los núcleos Zen 4

Leaked AMD documents confirm integrated GPUs for next-generation Socket AM5 processors

Fuente(s)

Top 10 Análisis

» Top 10 Portátiles Multimedia

» Top 10 Portátiles de Juego

» Top 10 Portátiles de Juego ligeros

» Top 10 Portátiles Asequibles de Oficina/Empresa

» Top 10 Portátiles de Juego Ligeros

» Top 10 Portátiles de Oficina/Empresa Premium

» Top 10 Estaciones de Trabajo

» Top 10 Subportátiles

» Top 10 Ultrabooks

» Top 10 Convertibles

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Tablets de menos de 250 Euros

» Top 10 Phablets (>5.5")

» Top 10 Smartphones

» Top 10 Smartphones (≤5")

» Top 10 Smartphones de menos de 300 Euros

» Top 10 Smartphones de menos de 120 Euros

» Top 10 Portátiles de menos de 1000 Euros

» Top 10 Portátiles de menos de 500 Euros

» Top 10 Portátiles de menos de 300 Euros

» Los Mejores Displays de Portátiles Analizados por Notebookcheck