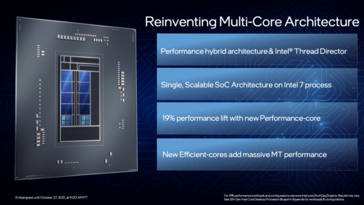

Después denumerosas rondas de filtracionespor fin está aquí. Intel ha presentado la nueva línea de procesadores Alder Lake-S de 12ª generación para ordenadores de sobremesa. Durante la presentación, Marcus Kennedy de Intel ofreció una visión general de lo que hace que Alder Lake funcione y cómo la arquitectura heterogénea compuesta por los núcleos Golden Cove Performance (P) y los núcleos Gracemont Efficiency (E) funcionan en el sistema.

Top 10 Análisis

» Top 10 Portátiles Multimedia

» Top 10 Portátiles de Juego

» Top 10 Portátiles de Juego ligeros

» Top 10 Portátiles Asequibles de Oficina/Empresa

» Top 10 Portátiles de Juego Ligeros

» Top 10 Portátiles de Oficina/Empresa Premium

» Top 10 Estaciones de Trabajo

» Top 10 Subportátiles

» Top 10 Ultrabooks

» Top 10 Convertibles

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Tablets de menos de 250 Euros

» Top 10 Phablets (>5.5")

» Top 10 Smartphones

» Top 10 Smartphones (≤5")

» Top 10 Smartphones de menos de 300 Euros

» Top 10 Smartphones de menos de 120 Euros

» Top 10 Portátiles de menos de 1000 Euros

» Top 10 Portátiles de menos de 500 Euros

» Top 10 Portátiles de menos de 300 Euros

» Los Mejores Displays de Portátiles Analizados por Notebookcheck

ISA heterogéneo, ahora en el escritorio principal

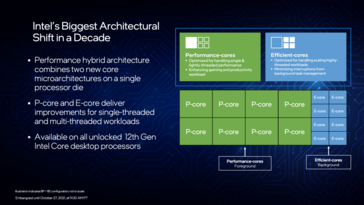

Intel afirma que los núcleos P están optimizados para aplicaciones de un solo hilo y de poco hilo, como juegos y tareas de productividad general en primer plano, mientras que los núcleos E están orientados a cargas de trabajo con muchos hilos. Los núcleos E también pueden ayudar a gestionar las tareas en segundo plano, mientras que los núcleos P se centran más en los aspectos de rendimiento. Esto no es muy diferente del enfoque big.LITTLE que los procesadores ARM han tenido durante años.

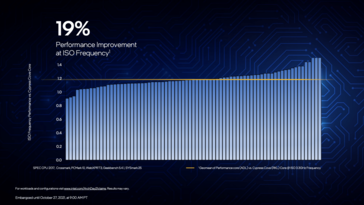

Intel afirma que este cambio de arquitectura puede ofrecer hasta un 19% de mejora respecto a la generación anterior de núcleos Cypress Cove en Rocket Lake a la misma frecuencia.

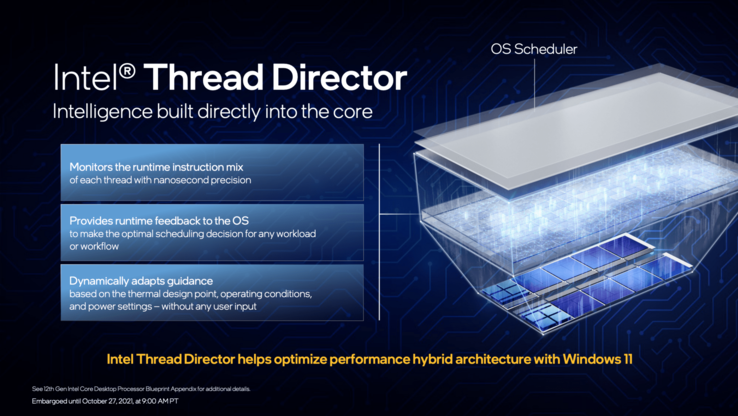

Director de hilos de Intel

Mientras que los sistemas operativos para móviles están construidos desde cero para ser conscientes de las arquitecturas heterogéneas, la situación es diferente en un ordenador de sobremesa. Por ello, Intel ha creado su propia forma de dirigir los hilos al núcleo correspondiente. Denominado Intel Thread Director, permite que el programador del sistema operativo sea consciente de la presencia de diferentes ISA en el mismo SoC y gestione eficazmente los recursos. Intel afirma que Thread Director tiene en cuenta varios parámetros, como el TDP, la potencia disponible, etc., y proporciona información continua al programador del sistema operativo con una "precisión de nanosegundos".

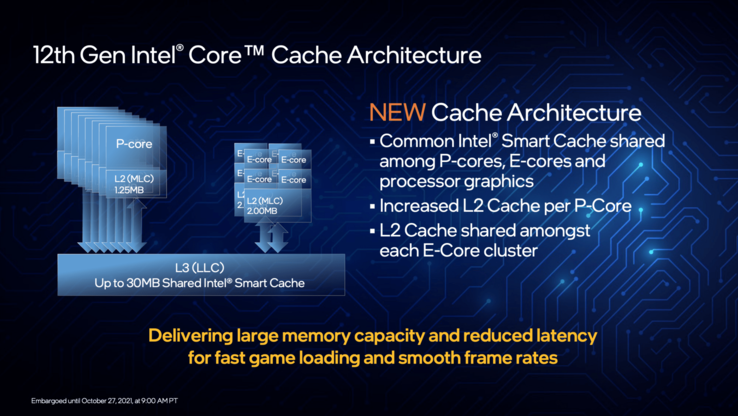

Caché L3 común de 30 MB para núcleos P y E

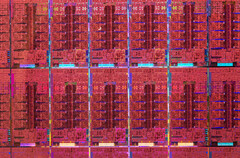

Dado el uso de dos ISA, Intel también ha modificado su topología de caché para la 12ª generación. La 11ª generación de Rocket Lake utilizaba núcleos Cypress Cove, que eran esencialmente Sunny Coves de 10 nm trasladados a 14 nm. Cypress Cove ofrecía ocho núcleos, cada uno con una caché L2 de 512 KB y una caché L3 de 2 MB. Con Alder Lake, cada núcleo P tiene una caché L2 de 1,25 MB, mientras que cada grupo de núcleos E tiene una caché L2 compartida de 2 MB. Creemos que esto significa que un conjunto de cuatro núcleos E compartiría una única caché L2, pero lo confirmaremos pronto con Intel.

Aparte de las cachés L2 dedicadas, Alder Lake también cuenta con una caché L3 compartida de 30 MB entre ambos tipos de núcleos y la GPU integrada para reducir la latencia. Aunque no se trata exactamente de una comparación de manzanas con manzanas, hemos visto cómo la caché L3 compartida ofrece ventajas de rendimiento inmediatas en el caso de los procesadores AMD Ryzen 5000 Zen 3.

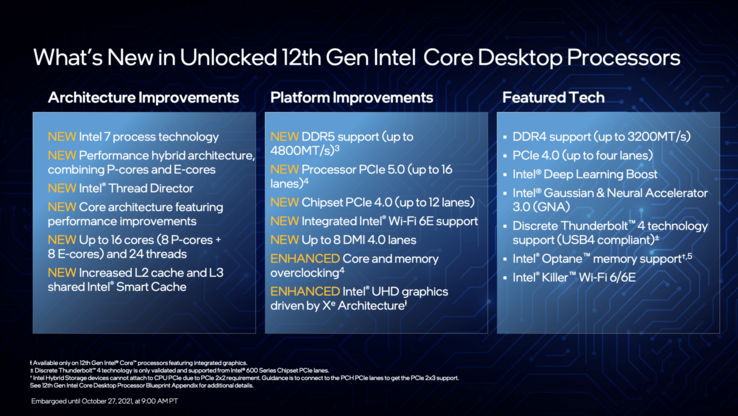

Características de la plataforma de 12ª generación - No hay PCIe Gen5 en el chipset

Alder Lake se basa en un proceso Enhanced SuperFin de 10 nm, ahora conocido como Intel 7. En el ordenador de sobremesa, el buque insignia Core i9-12900K ofrecerá hasta 16 núcleos y 24 hilos: 8 núcleos P que admiten hyperthreading y 8 núcleos E que no.

La CPU es compatible con la memoria RAM DDR5-4800,y también hemos visto varios anuncios de kits DDR5 por parte de los fabricantes de equipos originales. Dicho esto, la memoria DDR4-3200 también funciona bien

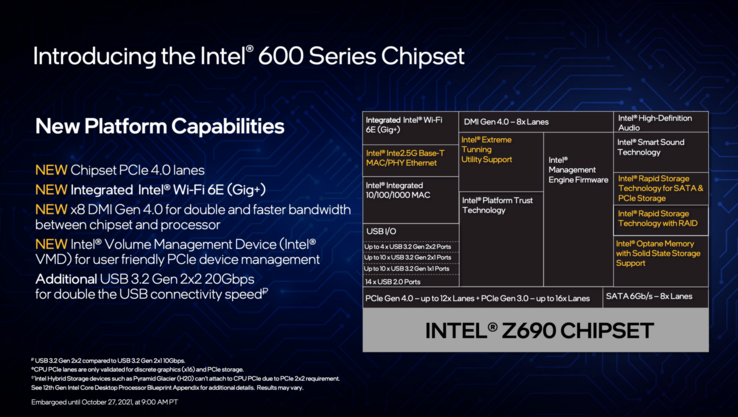

Los procesadores Alder Lake también ofrecen hasta 16 carriles de conectividad PCIe Gen5. Sin embargo, los chipsets de la serie 600 sólo admiten hasta 12 carriles de PCIe Gen4. Las razones exactas por las que se ha recortado el número de PCIe Gen5 en los chipsets de la serie 600, incluido el chipset insignia Z690, no están del todo claras. Podría ser que Intel pensara que esa implementación haría subir los precios, por no hablar del consumo de energía

Además, incluso una GPU como la NVIDIA GeForce RTX 3090 apenas puede saturar PCIe Gen3 x16. Dicho esto, el almacenamiento es un buen beneficiario del aumento de la E/S, por lo que podríamos ver algunas nuevas unidades NVMe que posiblemente puedan utilizar una buena cantidad del ancho de banda, que en caso de que te lo estés preguntando es de unos 128 GB/s agregados en 16 carriles.

En total, el chipset Z690 puede ofrecer hasta 28 carriles PCIe: 16 Gen3 y 12 Gen4. Además, hay ocho carriles para Direct Media Interface (DMI) 4.0. Para los que no lo sepan, DMI es un término elegante para el enlace entre el procesador y el hub controlador de la plataforma (PCH), es decir, el chipset (Northbridge y Southbridge, ¿alguien sabe?)

También es compatible con hasta 4 USB 3.2 Gen2x2, 10 USB 3.2 Gen2, 10 USB 3.2 Gen1 y 14 puertos USB 2.0, así que la conectividad no debería ser un problema. Por último, hay ocho carriles de puertos SATA 6 Gb/s para la expansión del almacenamiento

Fuente(s)

Informe de prensa de Intel