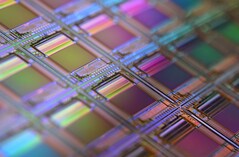

¿Y si su disco duro pudiera pensar con sus datos? En lugar de limitarse a almacenar archivos, imagínelo procesando y respondiendo a la información exactamente donde se guarda. Ése es el principio en el que se basa la informática en memoria, un cambio creciente en la arquitectura que acerca la lógica a la memoria para aumentar la eficiencia.

Ahora, investigadores del Forschungszentrum Jülich y de la Universidad de Duisburg-Essen han presentado un nuevo diseño basado en memristores 2T1R que podría apoyar este cambio, permitiendo una IA y un hardware de borde más eficientes energéticamente.

Publicado en arXivel diseño integra dos transistores y un memristor por celda, con regulación de corriente destinada a suprimir las corrientes de camino furtivo, un reto conocido en las matrices de memristores. A diferencia de las memorias convencionales, el diseño propuesto pone a tierra ambos terminales de los memristores cuando están inactivos, una estrategia que puede ayudar a mejorar la estabilidad de la señal y reducir las fugas.

La arquitectura está diseñada para soportar la multiplicación vectorial-matricial analógica (VMM), una función central en el aprendizaje automático, mediante el control de la conductancia de los memristores utilizando DAC integrados, señales PWM y rutas de corriente regulada. Se ha implementado con éxito una matriz de prueba de 2×2 utilizando tecnología CMOS estándar de 28 nm.

Al abordar los problemas de la tierra virtual y los efectos de la resistencia de los cables, la arquitectura pretende mejorar la previsibilidad del rendimiento y reducir el consumo de energía. Con compatibilidad para el control RISC-V y la interconexión digital, el diseño 2T1R puede sentar las bases para chips neuromórficos escalables, permitiendo una aceleración de la IA más rápida y compacta directamente dentro de la memoria.

Aunque puede que su disco duro aún no esté pensando, la arquitectura que hay detrás de esa visión ya está tomando forma en el silicio, lo que insinúa un futuro de IA más rápida e integrada en la memoria.

Para conocer todos los detalles técnicos y los resultados, consulte el preprint arXiv completo de (PDF).

Fuente(s)

Top 10 Análisis

» Top 10 Portátiles Multimedia

» Top 10 Portátiles de Juego

» Top 10 Portátiles de Juego ligeros

» Top 10 Portátiles Asequibles de Oficina/Empresa

» Top 10 Portátiles de Juego Ligeros

» Top 10 Portátiles de Oficina/Empresa Premium

» Top 10 Estaciones de Trabajo

» Top 10 Subportátiles

» Top 10 Ultrabooks

» Top 10 Convertibles

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Tablets de menos de 250 Euros

» Top 10 Phablets (>5.5")

» Top 10 Smartphones

» Top 10 Smartphones (≤5")

» Top 10 Smartphones de menos de 300 Euros

» Top 10 Smartphones de menos de 120 Euros

» Top 10 Portátiles de menos de 1000 Euros

» Top 10 Portátiles de menos de 500 Euros

» Top 10 Portátiles de menos de 300 Euros

» Los Mejores Displays de Portátiles Analizados por Notebookcheck